Projet M2 SETI

https://gitea.auro.re/higepi/Projet_SETI_RISC-V

Sujet

Dépôts & liens utilisables

Simulations

Choix du(/des) processeur risc-v

0. les processeurs utilisés :

on utilise un processeur RISC-V rv32im avec des extensions pour la mesure de performance

on utilise aussi un processeur superscalaire

1. les limites de la carte DE1-SOC

la carte DE1-SOC n’a pas été pensée pour faire du sofcore mais plutot pour faire du co-processing avec les ARM et du traitement de données sur le FPGA.

Ainsi la partie programmable (PL) n’a pas accès à la SDDRAM3 de la carte. elle a cependant accès a une SDRAM x16.

On note un acces a une interface JTAG qui nous permettra un debug plus facile.

Aussi la partie ARM consomme un nombre important des pins de la puce. Si on veut emuler un coeur de manière pratique et correcte on a donc deux choixs :

- un softcore sans interaction avec l’ARM et l’AXI bus, dans ce cas on utilisera seulement la SDRAM dans le FPGA pour gerer la mémoire.

- un softcore qui interagit avec l’ARM et l’AXI, on pourra ainsi chercher a avoir acces a la DDR3 de la carte.

on choisi en première otpion d’utiliser la ram interne au fpga pour gagner en simplicité

choix du risc

On trouve sur github pleins de projets dependants de compilateurs verilog hors IDE, ces projets sont souvent très élaborés et peu ompatibles avec des IDE comme quartus (dont les choixs de design sont parfois douteux)

si on se limite a des projets “simples” mais performant en vhdl on trouve quelques git.

Le plus pertinent pour sa documentation et la structure saine de son RTL nous est apparu etre NEORV32 un processeur 32 bits configurable et se limitant à une cinquantaine de fichiers vhdl.

- neorv32’s github

- neorv32’s datasheet

- neorv32’s user guide

PS:containing the RISCV HW synthesis, the compilation toolchain setup, and some SW tests.

implémentation simple

DONE :

- synthèse d’un proc sans bootloarder

- assignement of pins

- faire tourner un prpgramme simple

- mettre une lisaison serie fpga <-> UART via les ports GPIO (TX Carte sur PIN_Y17 = GPIO_O[1] (fil blanc), RX -> PIN_AC18 = GPIO_O[0] (fil vert), 5V 11e pin, GND 12e pin) https://cs.colby.edu/courses/F22/cs232-labs/DE1_User_Manual.pdf Device : Prolific Serial Port

- mettre une pll en entrée pour tourner à 100MHz

- mesures

TODO :

- passer a un processeur plus lourd (et adapter la toolchain)

- tester d’autres processeurs, darkriscv and biriscv

HOWTO :

- envoyer un programme sur la carte.

la carte fonctionne avec une ecriture en ROM. on ecrit le programme en RTL (un fichier VHDL), il sera ecrit en mémoire lors de l’implementation sur le FPGA.

Pour lancer le programme il suffit d’appuyer sur le bouton reset. \

Pour compiler votre fichier C en bianire et puis en VHDL à implémenter vous pouvez prendre exemple sur les makefile trouvable ici : “~/neorv32/sw/example/” \

La toolchain de compilation adapté au processeur est deja build sur la VM.

etape 1 . ecrire votre fichier C++/C

etape 2 . le compiler en binaire et ecrire ce binaire en VHDL (ispirez vous des make dans les exemples)

etape 3 . re-run la synthèse quartus.

etape 4 . programmer le FPGA

etape 5 appuyer sur le boutton reset (un des 4 bouttons poussoir en bas de la carte)

-

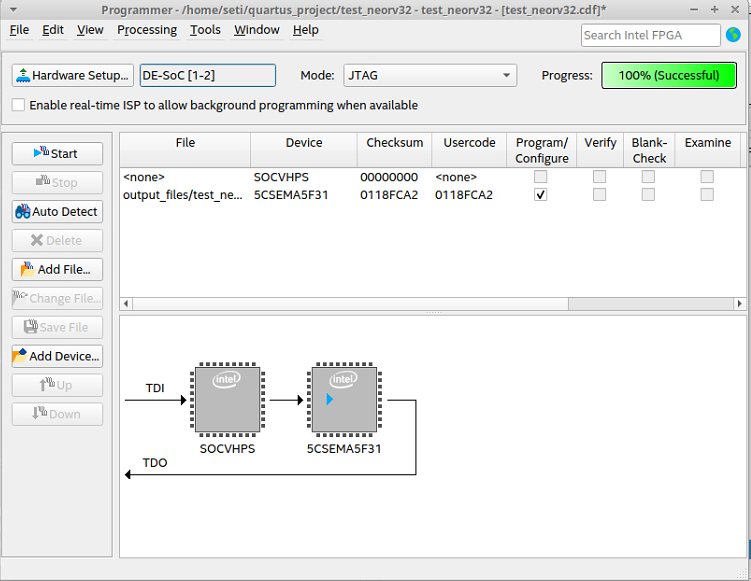

programmer le FPGA :

On programme sur la carte un fichier sof. ce fichier va laisse quartus trouver le fpga.

Il aura aussi besoin de trouver la partie ARM de la carte qui fait partie du circuit JTAG. le boutton auto-detect permet de l’ajouter.

-

utilisation du bootloader.

les ports series se trouve sur l’expansion header de la carte.

ON trouve sur ces ports 2 GND et deux sources de tension (une a 5V et un a 3.3V) les ports se trouvent sur le premier header gpio, le pin numero 0 est les RX du softcore, et le pin 1 est le TX.

LA DOCUMENTATION NE DONNE AUCUN INDICE SUR QUEL HEADER EST LE 0 ET LEQUEL EST LE 1? NI SUR LE SENS DE LECTURE DES PINS -

generation de la toolchain

aller dans la dir “~/riscv-gnu-toolchain”

executer la commande :./configure --prefix=/opt/riscv --with-arch=rv32i --with-abi=ilp32

ici on configure une toolchain pour une architecture riscv ne traitant que les entiers (sans multiplication et division entières.)

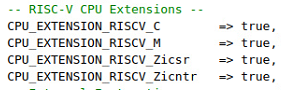

Dans le cas du processeur bootloarder on a les extensions suivantes :

on va donc utiliser la config suivante :

./configure --prefix=/opt/riscv --with-arch=rv32imc --with-abi=ilp32

on suit alors avec un make clean et un sudo make pour build la toolchain (cette opération peut prendre plus d’une heure)

ATTENTION : la configuration de la toolchain peut etre un sous ensemble de la configuration du cpu mais pas l’inverse. Un code compilé avec la toolchain du processeur le plus simple peut tourner sur le processeur bootloadé, mais pas l’inverse.

Utiliser le processeur ARM de la carte

Utiliser le simulateur

Requirement:

La toolchain riscV gnu

Ok si fait pour Quartus

rust/cargo

Suivre https://rustup.rs/

Usage:

Cloner ce dépot https://gitlab.com/leopold_clement/riscv-full-sim

Ne pas hésiter à pull la branch master et lancer “cargo t” pour vérifier que le simulateur passe ses tests.

Lancement d’un programme:

placer le code C ou assembleur dans benchmarck/bench.

Utiliser le makefile pour build :

bin/machinO1.ihexoubin/machinO2.ihexsi vous aviez le codebench/machin.cbin/machinasm.ihexsi bous aviez le code dansbench/machin.s.

Ensuite, vous pouvez lancer le simulateur avec le fichier binaire ihex :

cargo run -- -v -p benchmarck/bin/machinO1.ihex -l out.log

Les paramettres du simulateur sont apres les --.

Comment avoir un code qui termine:

Je fournis une fonction void halt() qui permet au code de signaler au simulateur que l’exécution est fini.